# **PCM-3780**

2-ch Counter/Timer with 24-channel TTL DIO Module

# **User Manual**

#### Copyright

The documentation and the software included with this product are copyrighted 2005 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

#### Acknowledgements

Windows is a trademark of Microsoft Corporation Inprise Delphi is a registered trademark of Inprise Corporation

All other product names or trademarks are properties of their respective owners.

Part No. 2003M37800 1st Edition Printed in Taiwan July 2005

#### **Two Years Product Warranty**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech.s high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- 1. Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandize authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

#### **CE** Notification

The PCM-3780, developed by Advantech Co., Ltd., has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **FCC Class A**

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

#### **Technical Support and Assistance**

- 1. Visit the Advantech web site at **www.advantech.com/support** where you can find the latest information about the product.

- Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

#### **Packing List**

Before setting up the system, check that the items listed below are included and in good condition. If any item does not accord with the table, please contact your dealer immediately.

The package should contain the following items:

- 1 x PCM-3780 DA&C card

- 1 x PCM-3780 User Manual

- 1 x Advantech DLL Drivers CD-ROM

# Contents

| Chapter | 1           | Introduction                                           | 2    |

|---------|-------------|--------------------------------------------------------|------|

| -       | 1.1         | Features                                               | . 2  |

|         |             | Table 1.1:PCM-3780 Counter Mode                        | 3    |

|         |             | Table 1.2:PCM-3780 Counter Mode                        | 4    |

|         | 1.2         | Applications                                           |      |

|         | 1.3         | Installation Guide                                     | 5    |

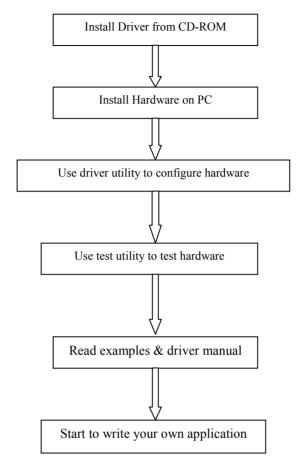

|         |             | Figure 1.1:Installation Flow Chart                     |      |

|         | 1.4         | Software Overview                                      | 7    |

|         |             | 1.4.1 Device Drivers (on the companion CD-ROM)         |      |

|         |             | 1.4.2 Device Drivers                                   |      |

|         |             | 1.4.3 Register-level Programming                       |      |

|         | 1.5         | Device Drivers Programming Roadmap                     | 8    |

|         |             | 1.5.1 Programming Tools                                |      |

|         |             | 1.5.2 Programming with Device Drivers Function Library |      |

|         |             | 1.5.3 Troubleshooting Device Drivers Error             |      |

|         | 1.6         | Accessories                                            | 10   |

|         |             | 1.6.1 Wiring Cables                                    |      |

|         |             | 1.6.2 Wiring Boards                                    | 10   |

| Chapter | 2           | Hardware Installation                                  | . 12 |

| -       | 2.1         | Unpacking                                              | 12   |

|         | 2.2         | Driver Installation                                    | 13   |

|         |             | Figure 2.1: The Setup Screen of Advantech Automati     | ion  |

|         |             | Software                                               | 13   |

|         |             | Figure 2.2:Different Options for Driver Setup          |      |

|         | 2.3         | Hardware Installation                                  |      |

|         | 2.5         | 2.3.1 Installing the Module                            |      |

| Chapter | 3           | Pin Assignments & Jumper Settings                      | . 18 |

| •       | 3.1         | Overview                                               |      |

|         | 3.2         | Signal Connections.                                    |      |

|         | J. <u>-</u> | Figure 3.1:Connectors Locations                        |      |

|         |             | Table 3.1:Connectors Table                             |      |

|         | 3.3         | Switch and Jumper Settings                             | 19   |

|         |             | Table 3.2:Base Address Setting                         | 20   |

|         | 3.4         | Connectors Pin Assignment                              | 21   |

|         |             | Figure 3.2:I/O Port Connector                          |      |

|         |             | Figure 3.3:Counter Interface Connector                 | 21   |

|         |             | Table 3.3:I/O Connector Signal Descriptions            | 22   |

|         | 3.5         | Period Measurement                                     | 23   |

|         |             | 3.5.1 Using Advantech 32-bit DLL Driver                |      |

|         |             | 3.5.2 Using Direct I/O                                 |      |

|         |             | Figure 3.4:Period Measurement                          |      |

|         | 3.6         | Frequency Measurement                                  | 24   |

|         |             | 3.6.1 Using Advantech 32-bit DLL Driver                | 24   |

|              | 3.6.2 Using Direct I/O                            | 24       |

|--------------|---------------------------------------------------|----------|

|              | Figure 3.5:Frequency Measurement                  |          |

| Appendix A   | Specifications                                    |          |

| A.1          | Programmable Counter                              |          |

| A.2          | Digital Input/Output                              | 20<br>26 |

| A.3          | General                                           |          |

| Appendix B   | Block Diagram                                     |          |

|              | _                                                 |          |

| Appendix C   | Register Structure & Format                       |          |

| C.1          | Overview                                          | 32       |

| C.2          | I/O Port Address Map                              |          |

|              | C.2.1 Register Format                             |          |

| ~ •          | Table C.1:Register Offset Address Table           | 33       |

| C.3          | Counter 0/1 Mode Register                         | 35       |

| C.4          | Counter 0/1 Load Register:                        | 37       |

| C.5          | Counter 0/1 Hold Register                         | 37       |

| C.6          | Counter 0/1 Command Register                      | 38       |

| C.7          | Counter Command Enable Register                   |          |

| C.8          | Interrupt Control Register                        | 39       |

| C.9          | Interrupt Status Register                         |          |

| C.10         | Interrupt Clear Register                          |          |

| C.11<br>C.12 | I/O Direction Control Register                    | 40       |

| C.12<br>C.13 | Port A/B/C Interrupt Status RegisterFOUT Register |          |

|              |                                                   |          |

| Appendix D   | Waveform of Each Mode                             |          |

| D.1          | Counter Mode Descriptions                         | 44       |

|              | Table D.1:PCM-3780 Counter Mode                   | 45       |

| D.1          | Table D.2:PCM-3780 Counter Mode                   |          |

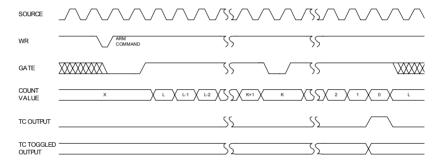

| D.2          | Mode A Waveforms                                  |          |

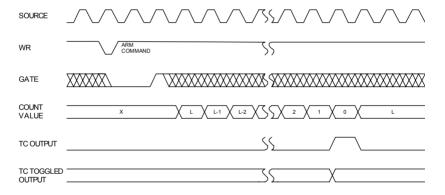

| D.3<br>D.4   | Mode B Waveforms                                  |          |

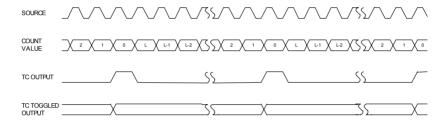

| D.4<br>D.5   | Mode D Waveforms                                  |          |

| D.5<br>D.6   | Mode E Waveforms                                  |          |

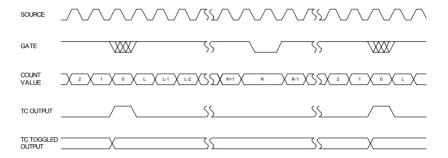

| D.0<br>D.7   | Mode F Waveforms                                  |          |

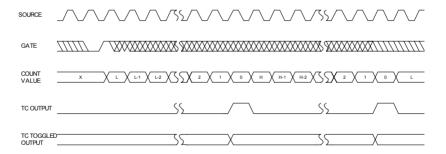

| D.7<br>D.8   | Mode G Waveforms                                  |          |

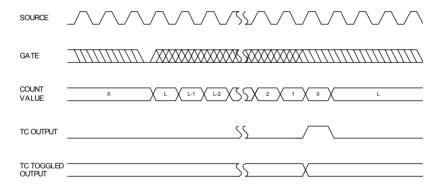

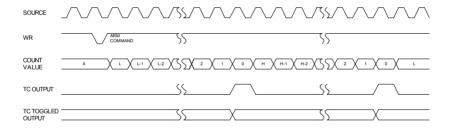

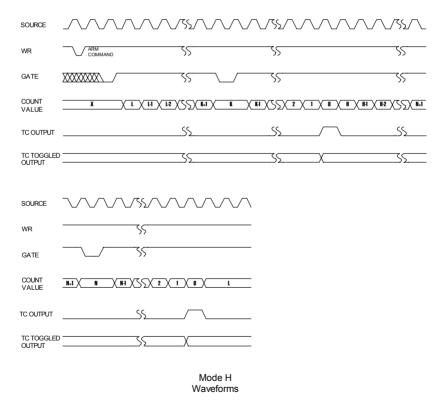

| D.8<br>D.9   | Mode H Waveforms                                  |          |

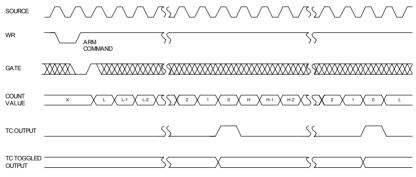

| D.10         | Mode I Waveforms                                  |          |

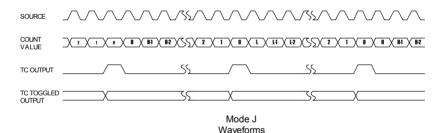

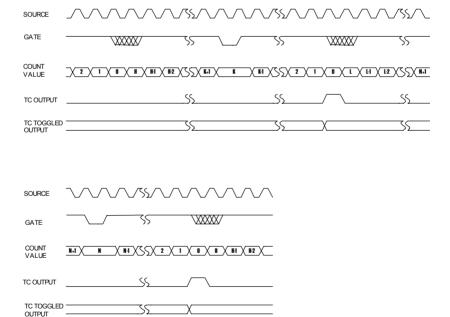

| D.10<br>D.11 | Mode J Waveforms                                  |          |

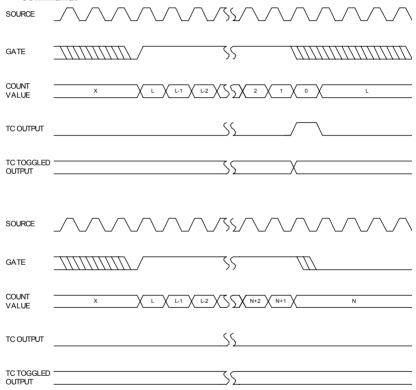

| D.11<br>D.12 | Mode K Waveforms                                  |          |

| D.12<br>D.13 | Mode L Waveforms                                  |          |

| D.13<br>D.14 | Mode O Waveforms                                  |          |

| D.15         | Mode R Waveforms                                  |          |

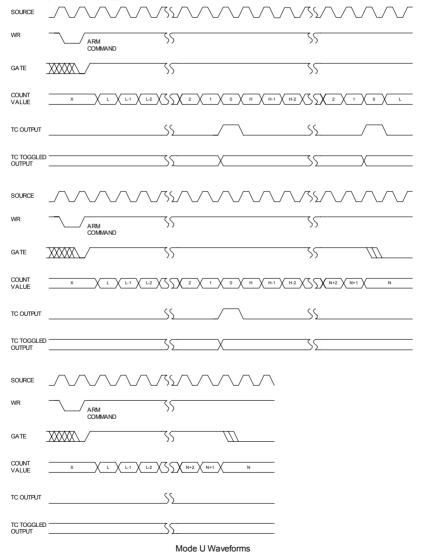

| D.16         | Mode U Waveforms                                  |          |

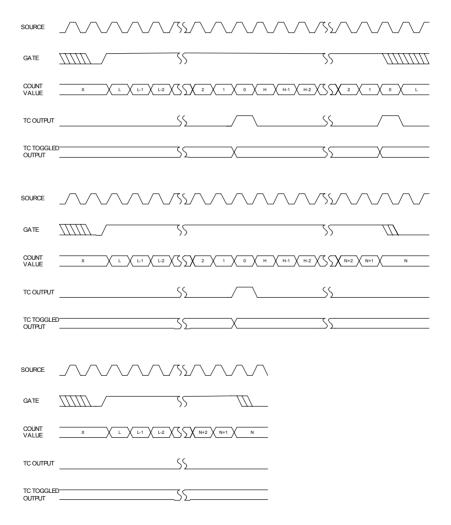

| D.17         | Mode X Waveforms                                  |          |

# Introduction

This chapter provides an introduction to the PCM-3780.

Sections include:

- Introduction

- Features

- Applications

- Installation Guide

- Accessories

# **Chapter 1 Introduction**

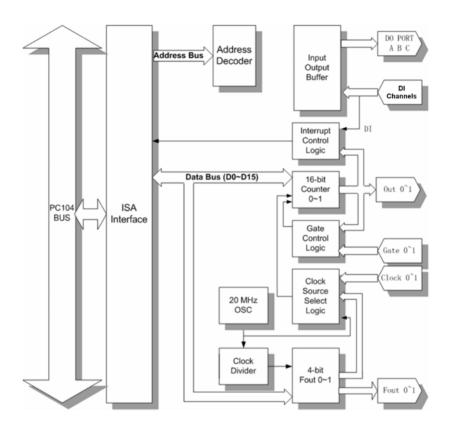

Thank you for buying the Advantech PCM-3780. The PCM-3780 is a general purpose multiple channel counter/timer card for the PC/104 bus. It targets the AM9513 to implement the counter/timer function by CPLD. It provides two 16-bit counter channels and 24-ch digital TTL I/O.

The I/O bits are divided into three 8-bit I/O ports: A0, B0 and C0. You can configure each port as either input or output via software. The powerful Advantech-designed counter functions fulfill your industrial or laboratory application needs.

The following sections of this chapter will provide further information about features of the multifunction cards, a quick startup guide for installation, together with some brief information on software for the PCM-3780 card.

#### 1.1 Features

The Advantech PCM-3780 offers the following main features:

- 2 independent 16-bit counters

- 2 programmable clock sources

- 24-ch digital TTL I/O

- Up to 20 MHz input frequency

- Multiple counter clock source selectable

- Counter output programmable

- · Counter gate function

- Flexible interrupt source select

## **Counter Modes**

| Table 1.1: PCM-3780 Cour                                                                      | nter | Mo | ode |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------------------------------------------------------|------|----|-----|---|---|---|---|---|---|---|---|---|

| Counter Mode                                                                                  | Α    | В  | С   | D | E | F | G | Н | I | J | K | L |

| Special Gate (CM6)                                                                            | 0    | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reload Source (CM5)                                                                           | 0    | 0  | 0   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| Repetition (CM4)                                                                              | 0    | 0  | 0   | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| Gate Control<br>(CM15~CM12)                                                                   | N    | L  | Е   | N | L | Е | N | L | Е | N | L | Е |

| Count to TC once, then disarm                                                                 | Υ    | Y  | Υ   |   |   |   |   |   |   |   |   |   |

| Count to TC twice, then disarm                                                                |      |    |     |   |   |   | Υ | Υ | Υ |   |   |   |

| Count to TC repeatedly without disarming                                                      |      |    |     | Υ | Υ | Υ |   |   |   | Υ | Υ | Υ |

| Gate input dose not gate counter input                                                        | Υ    |    |     | Υ |   |   | Υ |   |   | Υ |   |   |

| Count only during active gate level                                                           |      | Υ  |     |   | Υ |   |   | Υ |   |   | Υ |   |

| Start count on active gate edge and stop count on next TC                                     |      |    | Υ   |   |   | Y |   |   |   |   |   |   |

| Start count on active gate edge and stop count on second TC                                   |      |    |     |   |   |   |   |   | Υ |   |   | Υ |

| Start count on active gate edge and stop count on inactive gate edge                          |      |    |     |   |   |   |   |   |   |   |   |   |

| Reload counter from Load Register on TC                                                       | Υ    | Υ  | Υ   | Υ | Υ | Υ |   |   |   |   |   |   |

| Reload counter on each<br>TC, alternating reload<br>source between Load and<br>Hold Registers |      |    |     |   |   |   | Υ | Y | Υ | Υ | Υ | Υ |

(N: No gate control, L: Level gate control, E: Edge gate control)

| Table 1.2: PCM-3780 Cour                                                                      | nter | Mo | ode |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------------------------------------------------------|------|----|-----|---|---|---|---|---|---|---|---|---|

| Counter Mode                                                                                  | M    | N  | 0   | Р | Q | R | s | Т | U | ٧ | W | X |

| Special Gate (CM6)                                                                            | 0    | 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reload Source (CM5)                                                                           | 0    | 0  | 0   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| Repetition (CM4)                                                                              | 0    | 0  | 0   | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| Gate Control<br>(CM15~CM12)                                                                   | N    | L  | Е   | N | L | Е | N | L | Е | N | L | Е |

| Count to TC once, then disarm                                                                 | Y    | Υ  | Υ   |   |   |   |   |   |   |   |   |   |

| Count to TC twice, then disarm                                                                |      |    |     |   |   |   | Υ | Υ | Υ |   |   |   |

| Count to TC repeatedly without disarming                                                      |      |    |     | Υ | Υ | Υ |   |   |   | Υ | Υ | Υ |

| Gate input dose not gate counter input                                                        | Υ    |    |     | Υ |   |   | Υ |   |   | Υ |   |   |

| Count only during active gate level                                                           |      | Υ  |     |   | Υ |   |   | Υ |   |   | Υ |   |

| Start count on active gate edge and stop count on next TC                                     |      |    | Υ   |   |   | Υ |   |   |   |   |   |   |

| Start count on active gate edge and stop count on second TC                                   |      |    |     |   |   |   |   |   | Υ |   |   | Υ |

| Start count on active gate edge and stop count on inactive gate edge                          |      |    |     |   |   |   |   |   |   |   |   |   |

| Reload counter from Load Register on TC                                                       | Υ    | Υ  | Υ   | Υ | Υ | Υ |   |   |   |   |   |   |

| Reload counter on each<br>TC, alternating reload<br>source between Load and<br>Hold Registers |      |    |     |   |   |   | Υ | Υ | Υ | Υ | Υ | Υ |

**Note:** For detailed **specifications** of the PCM-3780, please refer to *Appendix A Specifications*.

# 1.2 Applications

- Event counting

- · One shot output

- Programmable frequency output

- · Frequency measurement

- Pulse width measurement

- · PWM output

- Periodic interrupt generation

- Time-delay generation

#### 1.3 Installation Guide

Before you install your PCM-3780 card, please make sure you have the following necessary components:

- PCM-3780 DA&C card

- PCM-3780 User Manual

- Driver software Advantech DLL drivers (included in the companion CD-ROM)

- Wiring cable: PCL-10120 & PCL-10150

- Wiring board: ADAM-3920 (Option) ADAM-3950 (Option)

- Computer Personal computer or workstation with a PC/104 slot (running Windows 2000/XP)

Some other optional components are also available for enhanced operation:

Application software ActiveDAQ, GeniDAQ or other third-party software packages

After you get the necessary components and maybe some of the accessories for enhanced operation of your Multifunction card, you can then begin the Installation procedures. Figure 1-1 on the next page provides a concise flow chart to give users a broad picture of the software and hardware installation procedures:

Figure 1.1: Installation Flow Chart

#### 1.4 Software Overview

Advantech offers a rich set of DLL drivers, third-party driver support and application software to help fully utilize the functions of your PCM-3780 card:

#### 1.4.1 Device Drivers (on the companion CD-ROM)

- · LabVIEW driver

- Advantech ActiveDAO

- · Advantech GeniDAO

Programming choices for DA&C cards: You may use Advantech application software such as Advantech Device Drivers. On the other hand, advanced users can use another option for register-level programming, although it is not recommended due to its laborious and time-consuming nature.

#### 1.4.2 Device Drivers

The Advantech Device Drivers software is included on the companion CD-ROM at no extra charge. It also comes with all Advantech DA&C cards. Advantech's device drivers feature a complete I/O function library to help boost your application performance. The Advantech

Device Drivers for Windows 2000/XP works seamlessly with development tools such as Visual C++, Visual Basic, Inprise C++ Builder and Inprise Delphi.

#### 1.4.3 Register-level Programming

Register-level programming is reserved for experienced programmers who find it necessary to write code directly at the level of device registers. Since register-level programming requires much effort and time, we recommend that you use the Advantech Device Drivers instead. However, if register-level programming is necessary, you should refer to the relevant information in Appendix C, Register Structure and Format, or to the example codes included on the companion CD-ROM.

## 1.5 Device Drivers Programming Roadmap

This section will provide a roadmap to demonstrate how to build an application from scratch using Advantech Device Drivers with your favorite development tools such as Visual C++, Visual Basic, Delphi and C++ Builder. The step-by-step instructions on how to build your own applications using each development tool will be given in the *Device Drivers Manual*. Moreover, a rich set of example source code is also given for your reference.

#### 1.5.1 Programming Tools

Programmers can develop application programs with the following tools:

- Visual C++

- · Visual Basic

- · Delphi

- C++ Builder

For instructions on how to begin programming works in each development tool, Advantech offers a *Tutorial* Chapter in the *Device Drivers Manual* for your reference. Please refer to the corresponding sections in this chapter of the *Device Drivers Manual* to begin your programming efforts. You can also look at the example source code provided for each programming tool, since they can get you very well oriented.

The *Device Drivers Manual* can be found on the companion CD-ROM. Or if you have already installed the Device Drivers on your system, The *Device Drivers Manual* can be readily accessed through the *Start* button:

Start/Programs/Advantech Automation/Device Manager /Device Driver's Manual

The example source codes could be found under the corresponding installation folder such as the default installation path:

\Program Files\Advantech\ADSAPI\Examples

For information about using other function groups or other development tools, please refer to the *Creating Windows 2000/XP Application with Device Drivers* chapter and the *Function Overview* chapter on the *Device Drivers Manual*.

## 1.5.2 Programming with Device Drivers Function Library

Advantech Device Drivers offers a rich function library to be utilized in various application programs. This function library consists of numerous APIs that support many development tools, such as Visual C++, Visual Basic, Delphi and C++ Builder.

According to their specific functions or services, those APIs can be categorized into several function groups:

- Digital Input/Output Function Group

- Counter Function Group

- Port Function Group (direct I/O)

- Event Function Group

For the usage and parameters of each function, please refer to the *Function Overview* chapter in the *Device Drivers Manual*.

#### 1.5.3 Troubleshooting Device Drivers Error

Driver functions will return a status code when they are called to perform a certain task for the application. When a function returns a code that is not zero, it means the function has failed to perform its designated function. To troubleshoot the Device Drivers error, you can pass the error code to **DRV\_GetErrorMessage** function to return the error message. Or you can refer to the *Device Drivers Error Codes* Appendix in the *Device Drivers Manual* for a detailed listing of the Error Code, Error ID and the Error Message.

#### 1.6 Accessories

Advantech offers a complete set of accessory products to support the PCM-3780 card. These accessories include:

#### 1.6.1 Wiring Cables

• PCL-10120

PCL-10120 cable is a 20-pin flat cable for PCM-3780 cards.

• PCL-10150

PCL-10150 cable is a 50-pin flat cable for PCM-3780 cards.

#### 1.6.2 Wiring Boards

The ADAM-3900 series consists of universal screw terminal modules designed for field signal wiring in industrial applications. They can be connected to the analog and digital ports of Advantech products such as the PCI, PCM and PCL series.

· ADAM-3920

ADAM-3920 is a 20-Pin Flat Cable Wiring Terminal.

ADAM-3950

ADAM-3950 is a 50-Pin Flat Cable Wiring Terminal.

# **Hardware Installation**

This chapter provides a packaged items checklist, proper instructions about unpacking and step-by-step procedures for card hardware installation.

# **Chapter 2 Hardware Installation**

## 2.1 Unpacking

After receiving your PCM-3780 package, please inspect its contents first. The package should contain the following items:

- PCM-3780 card

- Companion CD-ROM (DLL driver included)

- · User Manual

The PCM-3780 card has electronic components vulnerable to *electro-static discharge* (ESD). ESD could easily damage the integrated circuits and certain components if preventive measures are not carefully paid attention to. Before removing the card from the antistatic plastic bag, you should take following precautions to ward off possible ESD damage:

- Touch the metal part of your computer chassis with your hand to discharge static electricity accumulated on your body. Or use a grounding strap.

- Touch the anti-static bag to a metal part of your computer chassis before opening the bag.

- Take hold of the card only by the metal bracket when removing it from the bag.

After taking out the card you should first inspect the card for any possible signs of external damage (loose or damaged components, etc.). If the card is visibly damaged, please notify Advantech's service department or the local sales representative immediately. Avoid installing a damaged card into your system. Also, pay extra caution to the following aspects to ensure proper installation:

- Avoid physical contact with materials that could hold static electricity such as plastic, vinyl and Styrofoam.

- Whenever you handle the card, hold it only by its edges. DO NOT TOUCH the exposed metal pins of the connector or the electronic components.

Note

Keep the anti-static bag for future use. You might need the original bag to store the card if you have to remove the card from the PC or transport it elsewhere.

#### 2.2 Driver Installation

We recommend you to install the driver before you install the PCM-3780 card into your system, since this will guarantee a smooth installation process.

The Advantech Device Drivers Setup program for the PCM-3780 card is included on the companion CD-ROM that is shipped with your DA&C card package. Please follow the steps below to install the driver software:

**Step 1:** Insert the companion CD-ROM into your CD-ROM drive.

**Step 2:** The Setup program will be launched automatically if you have the autoplay function enabled on your system. When the Setup Program is launched, you'll see the following Setup Screen.

Note:

If the autoplay function is not enabled on your computer, use Windows Explorer or the Windows Run command to execute SETUP.EXE on the companion CD-ROM.

Figure 2.1: The Setup Screen of Advantech Automation Software

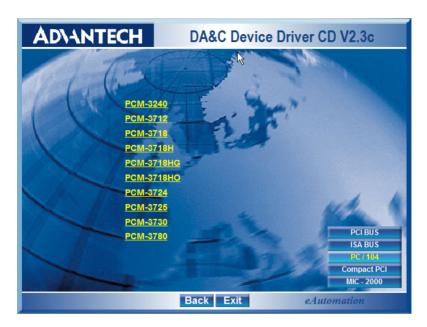

- **Step 3:** Select the Individual Drivers option.

- **Step 4:** Select the specific device then just follow the installation instructions step by step to complete your device driver setup.

Figure 2.2: Different Options for Driver Setup

For further information on driver-related issues, an online version of Device Drivers Manual is available by accessing the following path:

Start/Programs/Advantech Automation/Device Manager /Device Driver's Manual

#### 2.3 Hardware Installation

Note:

Make sure you have installed the driver before you install the card. We strongly recommend that you install the software driver before you install the hardware into your system, since this will guarantee a smooth and trouble-free installation process.

For more information about the driver installation, configuration and removal procedures for Windows 2000 and Windows XP, please see the corresponding help file:

After the DLL driver installation is completed, you can go on to install the PCM-3780 card in one of the PC/104 I slots on your computer. It is suggested that you refer to the computer user's manual or related documentation if you have any doubts. Please follow the steps below to install the card on your system.

#### 2.3.1 Installing the Module

- 1. Turn the PC's power off. Turn off the power of any peripheral devices such as printers and monitors.

- 2. Disconnect the power cord and any other cables from the back of the computer.

- 3. Remove the system unit cover (see the user.s guide for your chassis if necessary).

- 4. Remove the CPU card from the chassis (if necessary) to gain access to the card s PC/104 connector.

- Connect connector J1 of the PCM-3780 card to the PC/104 connector. Carefully align the pins with the PC/104 connector. Slide the module into the connector. The module pins may not slide all the way into the connector; do not force the pins into place, as the module may be damaged.

- 6. Fasten the module to the CPU card by using the included brass screw. Screw the brass spacer into the threaded hole on the CPU card. Do not tighten too much, or the threads may be damaged.

- 7. Attach any accessories to the PCM-3780 card using 20 pin cables.

- 8. Reinstall the CPU card and replace the system unit cover. Reconnect the cables you removed in step 2. Plug in and turn on the power.

# Pin Assignments & Jumper Settings

This chapter provides useful information about how to connect input and output signals to the PCM-3780 via the I/O connector.

#### Sections include:

- Overview

- · Signal Connections

- Switch & Jumper Settings

- Connectors Pin Assignment

- · Period Measurement

- Frequency Measurement

# Chapter 3 Pin Assignments & Jumper Settings

#### 3.1 Overview

Maintaining signal connections is one of the most important factors in ensuring that your application system is sending and receiving data correctly. A good signal connection can avoid unnecessary and costly damage to your PC and other hardware devices. This chapter provides useful information about how to connect input and output signals to the PCM-3780 via the I/O connector.

## 3.2 Signal Connections

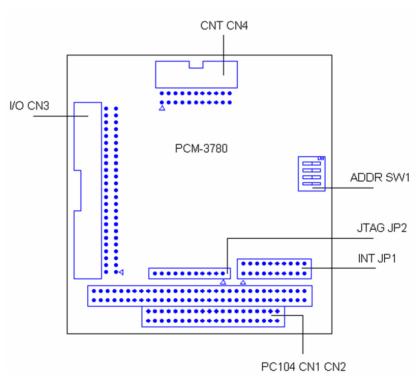

Figure 3.1: Connectors Locations

| Table 3.1 | Table 3.1: Connectors Table       |  |  |  |  |  |

|-----------|-----------------------------------|--|--|--|--|--|

| Label     | Function                          |  |  |  |  |  |

| CN1       | PC/104 Slot                       |  |  |  |  |  |

| CN2       | PC/104 Slot                       |  |  |  |  |  |

| CN3       | I/O Port Connector                |  |  |  |  |  |

| CN4       | Counter Interface Connector       |  |  |  |  |  |

| JP1       | Interrupt Jumper                  |  |  |  |  |  |

| JP2       | JTAG Connector                    |  |  |  |  |  |

| SW1       | Base Address Configuration Switch |  |  |  |  |  |

## 3.3 Switch and Jumper Settings

We designed PCM-3780 with ease-of-use in mind. It has one address switch and one interrupt jumper setting. The following section describes how to configure the card.

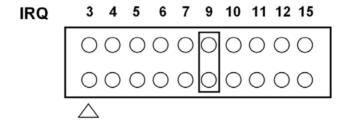

#### Interrupt Level (IRQ) Setting (JP1)

Select an IRQ which is not already in use by another card in the system. If you are installing more than one PCM-3780, set them to different IRQ numbers. Jumper bank JP1 controls the card IRQ. Simply place the jumper on the required interrupt level as shown in the following figure.

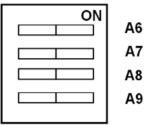

#### **Base Address Setting (SW1)**

Select an address which is not already in use by another card in the system. If you are installing more than one PCM-3780 card in your system, set the cards to different base addresses. The base address configuration switch SW1 controls each card's base address, as shown below.

**Switch ON:** Address Line Value = 0 **Switch OFF:** Address Line Value = 1

| Table 3.2: Base Address Setting |    |    |    |    |  |

|---------------------------------|----|----|----|----|--|

| Base Address                    | A6 | A7 | A8 | A9 |  |

| 100H — 13FH                     | 0  | 0  | 1  | 0  |  |

| 140H — 17FH                     | 1  | 0  | 1  | 0  |  |

|                                 |    |    |    |    |  |

| 3C0H — 3FFH                     | 1  | 1  | 1  | 1  |  |

For example:

Base Address 140H:

The following example shows how to set the base address to 140H.

The switch SW1 sum is set to 140H:

$$40H(A6=1) + 0(A7=0) + 100H(A8=1) + 0(A9=0) = 140$$

| Address Line | A6  | <b>A</b> 7 | A8   | A9   |

|--------------|-----|------------|------|------|

| HEX Value    | 40H | 80H        | 100H | 200H |

<sup>\*</sup>Default Setting = 300H

## 3.4 Connectors Pin Assignment

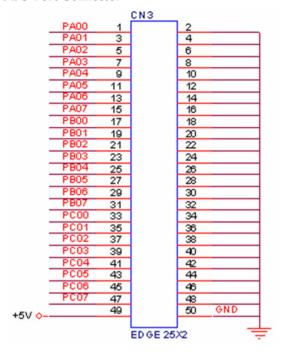

#### CN3: I/O Port Connector

Figure 3.2: I/O Port Connector

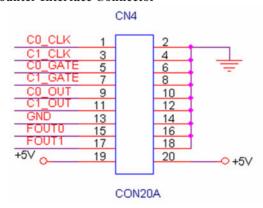

#### **CN4: Counter Interface Connector**

Figure 3.3: Counter Interface Connector

## I/O Connector Signal Description

| Table 3.3: I/O Connector Signal Descriptions |           |           |                                    |  |  |  |

|----------------------------------------------|-----------|-----------|------------------------------------|--|--|--|

| Signal Name                                  | Reference | Direction | Description                        |  |  |  |

| GND                                          | -         | -         | DC ground                          |  |  |  |

| +5V                                          | GND       | Output    | +5 VDC source                      |  |  |  |

| FOUT<01>                                     | GND       | Output    | Frequency output chan-<br>nels     |  |  |  |

| C_OUT<01>                                    | GND       | Output    | Counter output channels            |  |  |  |

| C_CLK<01>                                    | GND       | Input     | Clock external input chan-<br>nels |  |  |  |

| C_GATE<01>                                   | GND       | Input     | Gate control channels              |  |  |  |

| PA(/B/C)<07>                                 | GND       | I/O       | Digital I/O channels               |  |  |  |

#### 3.5 Period Measurement

#### 3.5.1 Using Advantech 32-bit DLL Driver

This approach is for a **low** frequency signal.

We recommend you to perform period measurement through our 32-bit DLL driver because it is the simplest way for both programming and wiring. Just connect the unknown single to **Gate** and the duty cycle will be measured by the software.

#### 3.5.2 Using Direct I/O

This approach is for a **low** frequency signal.

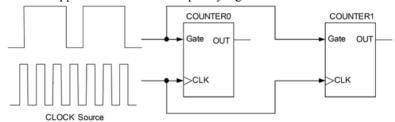

Figure 3.4: Period Measurement

Implementing this measurement needs two counters, one for the up cycle period and another for the down cycle period. These added together gives the total period. The duty cycle can also be calculated by dividing the up period with the total period. Connect the unknown signal to each counter's gate.

Apply a standard clock pulse to each counter. **Counter 0** counts the up cycle, while **Counter 1** counts the down cycle. In PCM-3780, wiring is simple. Just connect the unknown signal to **Counter 0**, and use the register to select the gate source. **Counter 0** selects "**Gate N**". **Counter 1** selects "**Gate N-1**".

Apply the standard clock to both counters with the clock source selection register. It can change the clock for different measurement ranges.

Counter 0 set as "Mode O" will make gate polarity positive. Counter 1 set as "Mode O" will make gate polarity negative.

#### 3.6 Frequency Measurement

#### 3.6.1 Using Advantech 32-bit DLL Driver

This approach is for a **high** frequency signal.

Measuring pulse frequency is simple by using the Advantech 32-bit DLL driver. Just connect the unknown single to **Gate** and the pulse frequency will be measured by the software.

#### 3.6.2 Using Direct I/O

This approach is for a high frequency signal.

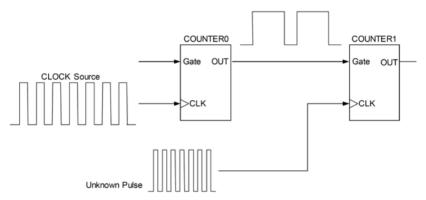

Figure 3.5: Frequency Measurement

It also takes two counters for frequency measurement. **Counter 0** counts the number of incoming standard source clock, while **Counter 1** counts the number of incoming unknown signal clock pulses.

Connect the standard clock source to **Gate** of **Counter 0** and set **Counter 0** to "**Mode D**". The total time period can be measured by **Counter 0** through the standard source clock (Multiply the number of incoming pulses by their frequency). Also connect the unknown signal to **CLK** of **Counter 1** and set **Counter 1** to "**Mode B**", and the frequency of the unknown signal can be calculated by dividing the number of pulses by the total time period.

# **Specifications**

This appendix provides detailed specifications for PCM-3780.

# **Appendix A Specifications**

# A.1 Programmable Counter

|                         | 1         |                            |  |  |  |  |  |

|-------------------------|-----------|----------------------------|--|--|--|--|--|

| Channels                | 2         |                            |  |  |  |  |  |

| Resolution              | 16-bit    | 16-bit                     |  |  |  |  |  |

| Compatibility           | TTL level |                            |  |  |  |  |  |

| Max. Input<br>Frequency | 20 MHz    |                            |  |  |  |  |  |

| Clask Issuet            | Low       | 0.8 V max.                 |  |  |  |  |  |

| Clock Input             | High      | 2.0 V min.                 |  |  |  |  |  |

| Cata lament             | Low       | 0.8 V max.                 |  |  |  |  |  |

| Gate Input              | High      | 2.0 V min.                 |  |  |  |  |  |

| Country Output          | Low       | 0.4 V max.@ +8.0mA (sink)  |  |  |  |  |  |

| Counter Output          | High      | 2.4 V min.@ -0.4mA(source) |  |  |  |  |  |

# A.2 Digital Input/Output

| Channels       | 24 (8255N | 24 (8255Mode 0)    |  |  |  |  |  |

|----------------|-----------|--------------------|--|--|--|--|--|

| Innut Valtage  | Low       | 0.4V max.          |  |  |  |  |  |

| Input Voltage  | High      | 2.4 V min.         |  |  |  |  |  |

| Innut I and    | Low       | 0.4 V max.@ -0.2mA |  |  |  |  |  |

| Input Load     | High      | 2.7 V min.@20µA    |  |  |  |  |  |

| Output Valtage | Low       | 0.5 V max.@+24 mA  |  |  |  |  |  |

| Output Voltage | High      | 2.4 V min.@-15 mA  |  |  |  |  |  |

# A.3 General

| I/O Connector Type   | One 50 pin and one 20 pin box header |                                                    |  |  |  |

|----------------------|--------------------------------------|----------------------------------------------------|--|--|--|

| Dimensions           | 90 x 96 mm (3.6" x 3.8")             |                                                    |  |  |  |

| Power<br>Consumption | Typical                              | +5 V @ 300mA                                       |  |  |  |

|                      | Max.                                 | +5 V @ 0.8A                                        |  |  |  |

| Temperature          | Operating                            | 0~+60° C (32~158° F)<br>(refer to IEC 68-2-1,2)    |  |  |  |

|                      | Storage                              | -20~+70° C(-4~158° F)                              |  |  |  |

| Relative Humidity    | Operating                            | 5~85 % RH non-condensing (refer to IEC 68-1,-2,-3) |  |  |  |

|                      | Storage                              | 5~95 % RH non-condensing (refer to IEC 68-1,-2,-3) |  |  |  |

| Certifications       | CE certified                         |                                                    |  |  |  |

APPENDIX BY

# **Block Diagram**

This chapter provides information on the block diagram for PCM-3780.

# **Appendix B Block Diagram**

# Register Structure & Format

This chapter provides information on the register structure and format for PCM-3780.

# Appendix C Register Structure & Format

### C.1 Overview

PCM-3780 is delivered with an easy-to-use 32-bit DLL driver for user programming under the Windows 2000/XP operating system. We advise users to program the PCM-3780 using the 32-bit DLL driver provided by Advantech to avoid the complexity of low-level programming by register.

The most important consideration in programming the PCM-3780 at register level is to understand the function of the card's registers. The information in the following sections is provided only for users who would like to do their own low-level programming.

# C.2 I/O Port Address Map

The PCM-3780 requires 64 consecutive addresses in the PC's I/O space. The address of each register is specified as an offset from the card's base address. For example, BASE+0 is the card's base address and BASE+6 is the base address plus six bytes.

Table C-1 shows the function of each register of the PCM-3780 or driver and its address relative to the card's base address.

# C.2.1 Register Format

| <i>Table</i><br>Base | e C.1 |          |           | er Of    |          |          |          | ble      |          |          |          |         |         |         |         |         |         |

|----------------------|-------|----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|---------|---------|---------|---------|---------|---------|

| Addre<br>HEX         | ess+  | 15       | 14        | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5       | 4       | 3       | 2       | 1       | 0       |

| 00h                  | W     |          |           | ) Mod    |          |          |          |          | 1        | 1        | 1        |         |         |         |         |         |         |

|                      |       | 15       | CM<br>14  | CM1<br>3 | CM1<br>2 | CM1<br>1 | CM1<br>0 | CM<br>9  | CM<br>8  | CM<br>7  | CM<br>6  | CM<br>5 | CM<br>4 | CM<br>3 | CM<br>2 | CM<br>1 | CM<br>0 |

|                      | R     | N/A      |           |          |          | •        |          |          |          |          |          |         |         |         |         |         |         |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

| 02h                  | W     | Cou      | nter (    | ) Load   | Regi     | ster     |          |          |          |          |          |         |         |         |         |         |         |

|                      |       | 15       | CL1<br>14 | CL13     | CL12     | CL11     | CL10     | CL9      | CL8      | CL<br>7  | CL<br>6  | CL<br>5 | CL<br>4 | CL<br>3 | CL<br>2 | CL<br>1 | CL<br>0 |

|                      | R     | N/A      |           |          |          | •        |          |          |          |          |          |         |         |         |         |         |         |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

| 04h                  | W     |          |           | ) Hold   |          |          | •        | •        |          |          |          |         |         |         | •       | •       |         |

|                      |       | CH<br>15 | CH1<br>14 | CH1<br>3 | CH1<br>2 | CH1<br>1 | CH1<br>0 | CH<br>9  | CH<br>8  | CH<br>7  | CH<br>6  | CH<br>5 | CH<br>4 | CH<br>3 | CH<br>2 | CH<br>1 | CH<br>0 |

|                      | R     | N/A      |           |          |          |          |          |          |          |          |          |         |         |         |         |         | 1       |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

| 06h                  | W     | Cou      | nter (    | ) Com    | mand     | Regis    | ster     |          |          |          |          |         |         | -       |         |         | 1       |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         | C2      | C1      | C0      |

|                      | R     | N/A      |           | l        |          | l        | 1        | 1        |          |          |          | 1       | 1       | 1       |         |         |         |

|                      | -     |          |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

| 08h                  | W     | Соп      | nter 1    | 1 Mod    | e Rea    | ister    |          |          |          |          |          |         |         |         |         |         |         |

| 0011                 |       |          |           | CM1      |          |          | CM1      | СМ       | СМ       | СМ       | СМ       | СМ      | СМ      | СМ      | СМ      | СМ      | СМ      |

|                      |       | 15       | 14        | 3        | 2        | 1        | 0        | 9        | 8        | 7        | 6        | 5       | 4       | 3       | 2       | 1       | 0       |

|                      | R     | N/A      |           |          |          |          |          |          |          |          |          |         |         |         | 1       | 1       |         |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

| A0h                  | W     | Cou      | nter 1    | Load     | Regi     | ster     |          |          |          |          |          |         |         |         |         |         |         |

|                      |       |          |           | CL13     |          |          | CL10     | CL9      | CL8      | CL       | CL       | CL      | CL      | CL      | CL      | CL      | CL      |

|                      |       | 15       | 14        |          |          |          |          |          |          | 7        | 6        | 5       | 4       | 3       | 2       | 1       | 0       |

|                      | R     | N/A      |           |          |          |          |          | 1        | 1        | 1        | 1        | 1       | 1       | 1       |         |         |         |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

| C0h                  | W     | Cou      | nter 1    | Hold     | Regis    | ster     | <u> </u> | <u> </u> | 1        | 1        | 1        | 1       | 1       | I       |         |         |         |

|                      |       |          |           | CH1<br>3 |          |          | CH1<br>0 | CH<br>9  | CH<br>8  | CH<br>7  | CH<br>6  | CH<br>5 | CH<br>4 | CH<br>3 | CH<br>2 | CH<br>1 | CH<br>0 |

|                      | R     | N/A      | l         |          |          |          |          | l        | I        | l        | I        | L       | L       | l       | l       | l       | l       |

|                      |       |          |           | 1        |          |          |          |          | 1        |          | 1        |         |         |         |         |         |         |

| E0h                  | W     | Cou      | nter 1    | Com      | mand     | Regis    | ster     |          |          |          |          |         |         |         |         |         |         |

|                      |       |          |           | 1        |          |          |          |          |          |          |          |         |         |         | C2      | C1      | C0      |

|                      | R     | N/A      |           |          |          |          |          |          |          |          |          |         |         |         |         |         |         |

|                      |       | ,, .     |           |          |          | I        |          |          |          |          |          |         |         |         |         |         |         |

| 20h                  | W     | Cou      | nter (    | Comm     | and F    | nable    | Regis    | ter      | 1        | 1        | 1        | L       | L       | L       |         |         |         |

| 2011                 |       | Jou      |           | 5011111  | and L    | . IGDIC  | . togic  |          |          |          |          |         |         |         |         | CE      | CE      |

|                      |       |          |           |          |          |          |          |          |          |          |          |         |         |         |         | 1       | 0       |

|                      | R     | N/A      | l         | l        |          | l        | l        | l        | 1        | 1        | 1        | 1       | 1       | 1       | L       | ١.      | ı -     |

|                      |       | , ١      |           |          |          |          |          |          |          |          |          |         |         |         | I       | I       | I       |

| <u> </u>             | 1     |          | <u> </u>  | L        |          | <u> </u> | <u> </u> |          | <u> </u> | <u> </u> | <u> </u> | 1       | 1       | L       | L       | L       | 1       |

|      |     | 1: Re  | egist  | er Of   | fset A  | 1 <i>ddre</i> | ss Ta | ble  |      |          |          |          |          |      |       |         |         |

|------|-----|--------|--------|---------|---------|---------------|-------|------|------|----------|----------|----------|----------|------|-------|---------|---------|

| 22h  | W   | Cou    | nter ( | Comm    | and E   | nable         | Regis | ster |      |          |          |          |          |      |       |         |         |

|      |     |        |        |         |         |               |       |      |      |          |          |          |          |      |       | CE<br>1 | CE<br>0 |

|      | R   | Inter  | runt   | Status  | Pagis   | etor          |       |      |      |          |          |          |          |      |       | '       | U       |

|      | 1   | IIILCI | Tupt   | Olalus  | rtegis  | SIC!          |       | I    |      | T        |          | 1        | וחו      | DIB  | DIA   | C1      | CO      |

|      |     |        |        |         |         |               |       |      |      |          |          |          | C.       | סוט  | D",   | Ŭ .     | 00      |

| 24h  | W   | Inter  | rupt   | Clear   |         |               |       |      |      |          |          |          |          |      |       |         |         |

|      |     |        |        |         |         |               |       |      |      |          |          |          |          |      |       |         |         |

|      | R   | N/A    |        |         |         | 1             | 1     | 1    | ı    |          |          |          | ,        |      |       |         | 1       |

| 2Ch  | W   | 1/0 [  | )iroc  | tion Co | ntrol   | Pagie         | tor   |      |      |          |          |          |          |      |       |         |         |

| 2011 | ٧٧  | 1/0 L  | JII CC | lion oc | Jillioi | rtegis        | lCi   | l    |      |          | 1        | T        | PA       | РС   | l l   | РΒ      | PC      |

|      |     |        |        |         |         |               |       |      |      |          |          |          | ' '      | H    |       |         | Ĺ       |

|      | R   | N/A    |        |         |         |               |       |      |      |          | -        |          |          | 1    | 1     | 1       |         |

|      |     |        |        |         |         |               |       |      |      |          |          |          |          |      |       |         |         |

| 2Eh  | W   | N/A    |        |         |         | ı             |       |      |      |          |          |          | ,        |      |       |         |         |

|      | R   | Dort   | A Int  | errupt  | Statu   | o Doo         | iotor |      |      |          |          |          |          |      |       |         |         |

|      | K   | FUIL   | A IIII | errupi  | Siaiu   | s Reg         | istei |      | Bit7 | Rit      | Rit      | Rif      | Rit      | Bit2 | Rit1  | RitO    | Rit7    |

|      |     |        |        |         |         |               |       |      | Ditt | 6        | 5        | 4        | 3        | DILL | Ditt  | Dito    | Diti    |

| 30h  | W   | N/A    |        |         |         |               |       | I    |      | 1        | <u> </u> |          |          |      | 1     | 1       | 1       |

|      |     |        |        |         |         |               |       |      |      |          |          |          |          |      |       |         |         |

|      | R   | Port   | B Int  | errupt  | Statu   | s Reg         | ister |      | D.12 | ъ.,      | ъ.,      | ъ.,      | ъ.,      | D:10 | D.1.4 | D.10    | D:17    |

|      |     |        |        |         |         |               |       |      | Bit7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit2 | Bit1  | BitO    | Bit/    |

| 32h  | W   | N/A    |        |         |         |               |       |      |      | U        | J        |          | J        | 1    |       |         |         |

|      | -   |        |        |         |         |               |       |      |      |          |          | T        |          |      |       |         |         |

|      | R   | Port   | C In   | terrupt | Statu   | s Reg         | ister | 1    | l .  | 1        | 1        |          | 1        | 1    | -     | -       | 1       |

|      |     |        |        |         |         |               |       |      | Bit7 |          |          | Bit      |          | Bit2 | Bit1  | Bit0    | Bit7    |

| 206  | ١٨/ | FOI    | ТОГ    | logioto |         |               |       |      |      | 6        | 5        | 4        | 3        |      |       |         |         |

| 38h  | W   | FUU    | HUF    | Registe | FOE     | ı             | FS2   | FS1  | EGU  | 1        |          | 1        | 1        | DV   | אחו   | DV      | אח      |

|      |     |        |        |         | IOL     |               | 1 32  | 131  | 1 30 |          |          |          |          | 3    | 2     | 1       | 0       |

|      | R   | N/A    |        |         |         |               |       |      |      |          |          |          |          |      |       |         |         |

|      |     |        |        |         |         |               |       |      |      |          |          |          |          |      |       |         |         |

| 3Ah  | W   | FOU    | T1 F   | Registe |         |               | 1     | ı    | ı    |          | 1        |          | 1        | ı    | 1     | 1       | 1       |

|      |     |        |        |         | FOE     |               | FS2   | FS1  | FS0  |          |          |          |          |      | DΛ    | DΛ      |         |

|      | R   | Dort   | Cle    | terrupt | Statu   | c Doo         | ictor |      |      |          |          |          |          | 3    | 2     | 1       | 0       |

|      | K   | PUIT   | C IN   | terrupt | Siaiu   | s Reg         | ister | I    | ı    |          |          | ı        | T        | 1    | 1     | 1       | 1       |

|      |     |        |        |         |         |               |       |      |      | <u> </u> |          | 1        |          |      |       |         |         |

# C.3 Counter 0/1 Mode Register

| Base         |   |       | 3780 R  | egister | Forma  | at   |      |    |    |    |    |    |    |    |    |    |    |

|--------------|---|-------|---------|---------|--------|------|------|----|----|----|----|----|----|----|----|----|----|

| Addr<br>+ HE | Χ |       | 14      | 13      | 12     | 11   | 10   | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| oh           | W | Count | er 0 Mo | de Re   | gister |      |      | •  | •  | •  | •  | •  | •  | •  | •  | •  |    |

|              |   | CM15  | CM14    | CM13    | CM12   | CM11 | CM10 | С  | С  | С  | С  | С  | CM | CM | СM | CM | СM |

|              |   |       |         |         |        |      |      | М9 | M8 | М7 | M6 | M5 | 4  | 3  | 2  | 1  | 0  |

|              | R | Count | er 0 Mo | de Re   | gister |      |      | •  | •  | •  | •  | •  | •  | •  | •  | •  | •  |

|              |   | CM15  | CM14    | CM13    | CM12   | CM11 | CM10 | С  | С  | С  | С  | С  | CM | CM | CM | CM | CM |

|              |   |       |         |         |        |      |      | М9 | M8 | Μ7 | M6 | M5 | 4  | 3  | 2  | 1  | 0  |

| 8h           |   |       | er 1 Mo |         | _      |      |      | •  | •  | •  | •  | •  | •  | •  | •  | •  | •  |

|              |   | CM15  | CM14    | CM13    | CM12   | CM11 | CM10 | С  | С  | С  | С  | С  | CM | CM | CM | CM | CM |

|              |   |       |         |         |        |      |      | М9 | M8 | Μ7 | M6 | M5 | 4  | 3  | 2  | 1  | 0  |

|              |   |       | er 1 Mo |         |        |      |      |    |    | •  | •  | •  | •  |    | •  | •  |    |

|              |   | CM15  | CM14    | CM13    | CM12   | CM11 | CM10 |    | С  | С  | С  | С  | CM | CM | CM | CM | CM |

|              |   |       |         |         |        |      |      | M9 | M8 | M7 | M6 | M5 | 4  | 3  | 2  | 1  | 0  |

### 1. CM1 to CM0: Output Control

- **00** = Active High Terminal Count Pulse

- 01 = Active Low Terminal Count Pulse

- 10 = TC Toggled from low

- 11 = TC Toggled from high

### 2. CM2: Output Enable Control

- **0** = Disable Output (High impedance)

- 1 = Enable Output

### 3. CM6 to CM3: Count Control

### CM6:

- **0** = Disable edge disarm in edge gate mode

- 1 = Enable edge disarm in edge gate mode

### CM5:

- 0 =Reload from Load

- 1 = Reload from Load or Hold

### CM4·

- 0 = Count Once

- 1 = Count Repetitively

### CM3:

- 0 = Count Down

- 1 = Count Up

### 4. CM7: Count Source Edge

- $\mathbf{0}$  = Count on Rising Edge

- 1 = Count on Falling Edge

### 5. CM11 to CM8: Count Source Selection

- **0000** = Internal Clock (20MHz)

- 0001 = OUT N-1

- 0010 = CLK N

- 0011 = CLK N-1

- 0100 = FOUT0

- **0101** = FOUT1

- 0111 = GATE N-1

### 6. CM13 to CM12: Gate Source Selection

- 00 = No Gating

- 01 = OUT N-1

- 10 = GATE N

- 11 = GATE N-1

# 7. CM14: Gating Polarity Selection

- **0** = High Level for Level Active, Rising Edge for Edge Active

- 1 = Low Level for Level Active, Falling Edge for Edge Active

# 8. CM15: Gate Active Edge or Level

- 0 = Level Active

- 1 = Edge Active

# C.4 Counter 0/1 Load Register:

| Base         |   |      | 3780   | Regist | er For | mat  |          |         |         |         |         |         |         |         |         |         |         |

|--------------|---|------|--------|--------|--------|------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Addr<br>+ HE | Χ |      | 14     | 13     | 12     | 11   | 10       | 9       | 8       | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| 2h           |   |      |        | oad R  |        |      | •        | •       | •       | •       |         | •       |         | •       |         | •       |         |

|              |   | CL15 | CL14   | CL13   | CL12   | CL11 | CL1<br>0 | CL<br>9 | CL<br>8 | CL<br>7 | CL<br>6 | CL<br>5 | CL<br>4 | CL<br>3 | CL<br>2 | CL<br>1 | CL<br>0 |

|              | R | Coun | er 0 L | oad R  | egiste | ſ    |          |         |         |         |         |         |         |         |         |         |         |

|              |   |      |        |        |        |      |          |         |         |         |         |         |         |         |         |         |         |

| Ah           | W |      |        | oad R  |        |      |          |         |         |         |         |         |         |         |         |         |         |

|              |   |      |        | CL13   |        |      | CL1<br>0 | CL<br>9 | CL<br>8 | CL<br>7 | CL<br>6 | CL<br>5 | CL<br>4 | CL<br>3 | CL<br>2 | CL<br>1 | CL<br>0 |

|              | R | Coun | er 1 L | oad R  | egiste | ſ    |          |         |         |         |         |         |         |         |         |         |         |

|              |   |      |        |        |        |      |          |         |         |         |         |         |         |         |         |         |         |

1. CL15 to CL0: Counter load data

# C.5 Counter 0/1 Hold Register

| Base |       | РСМ  | -3780  | ) Rea | ister I | -orma | at  |    |    |    |    |    |    |     |     |     |     |

|------|-------|------|--------|-------|---------|-------|-----|----|----|----|----|----|----|-----|-----|-----|-----|

| Addr | ,<br> | 4 E  |        |       | 13101 1 | 44    |     | _  | 0  | 7  | _  | _  |    | 2   | 2   | ı a |     |

| + HE | X     |      | 14     | 13    | 12      | 11    | 10  | 9  | 8  | 1  | 6  | 5  | 4  | 3   | 2   | ı   | U   |

| 4h   | W     | Cour | iter 0 | Hold  | Regis   | ster  |     |    |    |    |    |    |    |     |     |     |     |

|      |       | CH1  | CH1    | CH1   | CH1     | CH1   | CH1 | CH | CH | CH | CH | CH | CH | CH3 | CH2 | CH1 | CH0 |

|      |       | 5    | 4      | 3     | 2       | 1     | 0   | 9  | 8  | 7  | 6  | 5  | 4  |     |     |     |     |

|      | R     | Cour | iter 0 | Hold  | Regis   | ster  |     |    |    |    |    |    |    |     |     |     |     |

|      |       |      |        |       |         |       |     |    |    |    |    |    |    |     |     |     |     |

| Ch   | W     | Cour | iter 1 | Hold  | Regis   | ster  | •   | •  | •  |    | •  | •  |    | •   | •   | •   | •   |

|      |       | CH1  | CH1    | CH1   | CH1     | CH1   | CH1 | CH | CH | CH | CH | CH | CH | CH3 | CH2 | CH1 | CH0 |

|      |       | 5    | 4      | 3     | 2       | 1     | 0   | 9  | 8  | 7  | 6  | 5  | 4  |     |     |     |     |

|      | R     | Cour | iter 1 | Hold  | Regis   | ster  |     | •  | ,  |    |    |    |    |     |     |     |     |

|      |       |      |        |       |         |       |     |    |    |    |    |    |    |     |     |     |     |

<sup>1.</sup> CH15 to CH0: Counter hold data

# C.6 Counter 0/1 Command Register

| Base        |       | PCN                        | <i>1</i> -378 | 0 Re | gister | Form  | nat    |   |   |   |   |   |   |          |    |    |    |

|-------------|-------|----------------------------|---------------|------|--------|-------|--------|---|---|---|---|---|---|----------|----|----|----|

| Addr<br>HEX | ess + | 15                         | 14            | 13   | 12     | 11    | 10     | 9 | 8 | 7 | 6 | 5 | 4 | 3        | 2  | 1  | 0  |

| 6h          | W     | Cou                        | nter 0        | Com  | man    | d Reg | gister |   |   |   |   |   |   |          | 1  |    | "  |

|             |       |                            |               |      |        |       |        |   |   |   |   |   |   |          | C2 | C1 | C0 |

|             | R     | Counter 0 Command Register |               |      |        |       |        |   |   |   |   |   | 1 | <u> </u> | ·  |    |    |

| Eh          | W     | Cou                        | nter 1        | Com  | man    | d Reg | gister |   |   |   |   |   |   |          |    |    |    |

|             |       |                            |               |      |        |       |        |   |   |   |   |   |   |          | C2 | C1 | C0 |

|             | R     | Cou                        | nter 1        | Com  | man    | d Reg | gister |   | 1 | 1 |   |   |   | 1        | 1  |    |    |

|             |       |                            |               |      |        |       |        |   |   |   |   |   |   |          |    |    |    |

### 1. C2 to C0: Command Code

**000** = Disarm counter

**001** = Load counter from LOAD

010 = Disarm and Save counter

100 = Arm counter

101 = Load and Arm counter

110 = Save counter to HOLD

111 = Reset counter

# C.7 Counter Command Enable Register

| Base            |   | PCN | Л-37                           | 80 F | Regis | ter F | orm  | at  |      |     |   |   |   |   |   |     |     |

|-----------------|---|-----|--------------------------------|------|-------|-------|------|-----|------|-----|---|---|---|---|---|-----|-----|

| Addres<br>+ HEX |   | 15  | 14                             | 13   | 12    | 11    | 10   | 9   | 8    | 7   | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

| 20h             | W | Cou | punter Command Enable Register |      |       |       |      |     |      |     |   |   |   |   |   |     |     |

|                 |   |     |                                |      |       |       |      |     |      |     |   |   |   |   |   | CE1 | CE0 |

|                 | R | Cou | nter                           | Con  | nma   | nd E  | nabl | e R | egis | ter |   |   |   |   |   |     |     |

|                 |   |     |                                |      |       |       |      |     |      |     |   |   |   |   |   |     |     |

### 1. CE1 to CE0: Counter Command Enable Bit

**0** = Not Select this counter

1 = Select this counter

# **C.8 Interrupt Control Register**

| Base          |      | PCM   | 1-378                   | 0 Re | giste | r For | mat |   |   |   |   |   |     |     |     |    |    |

|---------------|------|-------|-------------------------|------|-------|-------|-----|---|---|---|---|---|-----|-----|-----|----|----|

| Addres<br>HEX | ss + | 15    | 14                      | 13   | 12    | 11    | 10  | 9 | 8 | 7 | 6 | 5 | 4   | 3   | 2   | 1  | 0  |

| 22h           | W    | Inter | errupt Control Register |      |       |       |     |   |   |   |   |   |     |     |     |    |    |

|               |      |       |                         |      |       |       |     |   |   |   |   |   | DIC | DIB | DIA | C1 | C0 |

|               | R    |       | •                       | •    | •     | •     |     |   |   |   |   |   | •   | •   | •   |    | •  |

|               |      |       |                         |      |       |       |     |   |   |   |   |   |     |     |     |    |    |

### 1. C1 to C0: Counter Interrupt enable Bit

- **0** = Not enable interrupt for this counter

- **1** = Enable interrupt for this counter

### 2. DIA, DIB and DIC: DI Interrupt enable Bit

- $\mathbf{0}$  = Not enable interrupt for DI

- 1 = Enable interrupt for DI

# C.9 Interrupt Status Register

| Base           |   | PCI  | M-37 | 780   | Reg  | istei | · Foi | ma | at |   |   |   |     |     |     |    |    |

|----------------|---|------|------|-------|------|-------|-------|----|----|---|---|---|-----|-----|-----|----|----|

| Addre<br>+ HEX |   | 15   | 14   | 13    | 12   | 11    | 10    | 9  | 8  | 7 | 6 | 5 | 4   | 3   | 2   | 1  | 0  |

| 22h            | W |      |      |       |      |       |       |    |    |   |   |   |     |     |     |    |    |

|                |   |      |      |       |      |       |       |    |    |   |   |   |     |     |     |    |    |

|                | R | Inte | rrup | t Sta | atus | Reg   | giste | r  |    |   |   |   |     |     |     |    |    |

|                |   |      |      |       |      |       |       |    |    |   |   |   | DIC | DIB | DIA | C1 | C0 |

# 1. C1 to C0: Counter Interrupt Status Bit

- $\mathbf{0}$  = No interrupt occur

- 1 = Interrupt occur

# 2. DIA, DIB and DIC: Interrupt Status Bit

- **0** = No interrupt occurred

- 1 = Interrupt occured

# C.10 Interrupt Clear Register

Write any data to these two bytes to clear the interrupt.

| Base            |    | PCN   | 1-378          | 0 Re | gister | Forr | nat |   |   |   |   |   |   |   |   |   |   |

|-----------------|----|-------|----------------|------|--------|------|-----|---|---|---|---|---|---|---|---|---|---|

| Addres<br>+ HEX | SS | 15    | 14             | 13   | 12     | 11   | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 24h             | W  | Inter | nterrupt Clear |      |        |      |     |   |   |   |   |   |   |   |   |   |   |

|                 |    |       |                |      |        |      |     |   |   |   |   |   |   |   |   |   |   |

|                 | R  |       |                |      | •      |      |     |   |   | • | • |   |   |   |   |   |   |

|                 |    |       |                |      |        |      |     |   |   |   |   |   |   |   |   |   |   |

# C.11 I/O Direction Control Register

| Base          |   | PC                             | M-3  | 780   | Reg  | istei | · Fo | rma  | ıt  |   |   |   |    |     |   |    |     |

|---------------|---|--------------------------------|------|-------|------|-------|------|------|-----|---|---|---|----|-----|---|----|-----|

| Addres<br>HEX |   |                                |      | 13    |      |       | 10   | 9    | 8   | 7 | 6 | 5 | 4  | 3   | 2 | 1  | 0   |

| 2Ch           | W | I/O Direction Control Register |      |       |      |       |      |      |     |   |   |   |    |     |   |    |     |

|               |   |                                |      |       |      |       |      |      |     |   |   |   | PA | PCH |   | PB | PCL |

|               | R | I/O                            | Dire | ectio | n Co | ontro | l R  | egis | ter |   |   |   | •  |     |   | •  |     |

|               |   |                                |      |       |      |       |      |      |     |   |   |   | PA | PCH |   | РВ | PCL |

### 1. I/O Direction Control Bit:

0 = Output

1 = Input

# C.12 Port A/B/C Interrupt Status Register

| Base            |   | PCM  | 1-378 | 30 Re | giste  | r Fo   | rma | t    |    |      |      |      |      |      |      |      |      |

|-----------------|---|------|-------|-------|--------|--------|-----|------|----|------|------|------|------|------|------|------|------|

| Addres<br>+ HEX |   | 15   | 14    | 13    | 12     | 11     | 10  |      | 8  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 2Eh             | W | Port | A In  | terru | ot Sta | itus I | Reg | iste | er | •    | •    | •    |      | •    | •    |      |      |

|                 |   | N/A  |       |       |        |        |     |      |    |      |      |      |      |      |      |      |      |

|                 | R | Port | A In  | terru | ot Sta | itus I | Reg | iste | er |      |      |      |      |      |      |      |      |

|                 |   |      |       |       |        |        |     |      |    | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 30h             | W | Port | B In  | terru | ot Sta | itus I | Reg | iste | r  | ı    |      |      |      |      |      |      |      |

|                 |   | N/A  |       |       |        |        |     |      |    |      |      |      |      |      |      |      |      |

|                 | R | Port | B In  | terru | ot Sta | itus I | Reg | iste | er |      |      |      |      |      |      |      |      |

|                 |   |      |       |       |        |        |     |      |    | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 32h             | W | Port | C In  | terru | ot Sta | itus   | Reg | iste | r  |      |      |      |      |      |      |      |      |

|                 |   | N/A  |       |       |        |        |     |      |    |      |      |      |      |      |      |      |      |

|                 | R | Port | C In  | terru | ot Sta | atus   | Reg | iste | er |      |      |      |      |      |      |      |      |

|                 |   |      |       |       |        |        |     |      |    | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

# 1. Bit7 to Bit0: Port A/B/C Interrupt Status Register

$\mathbf{0}$  = No interrupt occurred

1 = Interrupt occurred

# C.13 FOUT Register

| Base             | !                | PCI | M-37 | 80 F | Registe | er F | orma | at  |     |   |   |   |   |     |     |     |     |

|------------------|------------------|-----|------|------|---------|------|------|-----|-----|---|---|---|---|-----|-----|-----|-----|

| Address<br>+ HEX |                  | 15  | 14   | 13   | 12      | 11   | 10   | 9   | 8   | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

| 38h              | W FOUT0 Register |     |      |      |         |      |      |     |     |   | 1 |   |   |     |     |     |     |

|                  |                  |     |      |      | FOE     |      | FS2  | FS1 | FS0 |   |   |   |   | DV3 | DV2 | DV1 | DV0 |

|                  | R FOUT0 Register |     |      |      |         |      |      |     |     |   |   |   |   |     |     |     |     |

|                  |                  |     |      |      | FOE     |      | FS2  | FS1 | FS0 |   |   |   |   | DV3 | DV2 | DV1 | DV0 |

| 3Ah              | W                | FO  | JT1  | Reg  | ister   |      |      |     |     |   |   |   |   |     |     | 1   |     |

|                  |                  |     |      |      | FOE     |      | FS2  | FS1 | FS0 |   |   |   |   | DV3 | DV2 | DV1 | DV0 |

|                  | R                | FO  | JT1  | Reg  | ister   |      |      | •   | •   |   |   |   |   |     |     | •   |     |

|                  |                  |     |      |      | FOE     |      | FS2  | FS1 | FS0 |   |   |   |   | DV3 | DV2 | DV1 | DV0 |

### 1. DV3 to DV0: FOUT Divider (Divide by 1 to 16)

0000 = Divide by 1

0001 = Divide by 2

0010 = Divide by 3

0011 = Divide by 4

0100 = Divide by 5

0101 = Divide by 6

**0110** = Divide by 7

**0111** = Divide by 8

**1000** = Divide by 9

**1001** = Divide by 10

**1010** = Divide by 11

**1011** = Divide by 12

**1100** = Divide by 13

**1101** = Divide by 14

**1110** = Divide by 15

**1111** = Divide by 16

### 2. FS2 to FS0: FOUT Source

001 = CLK N

010 = FOUT N-1

011 = 10 MHz clock

**100** = 1 MHz clock

**101** = 100 KHz clock

**110** = 10 KHz clock

111 = 1KHz clock

## 3. FOE: FOUT Output Enable

**0** = Disable Output

1 = Enable Output

APPENDIX

# Waveform of Each Mode

The PCM-3780 offers 16 powerful counter functions for your industrial or laboratory applications. This chapter will describe each mode in detail with waveform diagrams.

# Appendix D Waveform of Each Mode

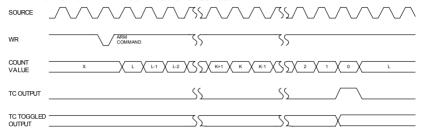

# **D.1 Counter Mode Descriptions**